# ECE 424 – INTRODUCTION TO VLSI DESIGN + LAB

# LABORATORY WORK 6

In this laboratory work, we will try to understand multiplexers, decoders and encoders by writing their vhdl codes.

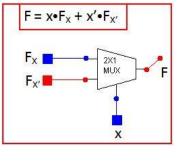

1) Figure 1 is explaining the working principle of a 2x1 multiplexer. The digital logic formula is also given in figure. We will write behavioral vhdl codes of this multiplexer together;

```

20

library IEEE;

21

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

22

23

24

25

entity mux2x1 is

26

Port ( a : in STD LOGIC;

27

b : in STD_LOGIC;

28

29

s : in STD_LOGIC;

Y : out STD LOGIC);

30

end mux2x1;

31

32

33

architecture Behavioral of mux2x1 is

34

begin

35

36

37

process (a,b,s)

38

39

40

begin

41

if s='0' then Y<=a;

42

43

44

else Y<=b;

45

46

end if;

47

48

end process;

49

50

Figure 2

```

Write the codes in figure 2 by opening a new project on your computer. Simulate it and verify the results by using simulation result.

Then write a 4x1 multiplexer by using this information. Open a new project for this program. Don't use the same project folder.

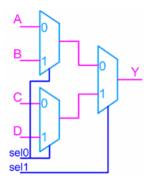

2) If you want to use the programs that you had written before in a new project, you can do it by adding a "component" to your project. You wrote a 4x1 mux during first part, but you can also write this program by using 2x1 mux.

Figure 3

Figure 3 is explaining this condition. If you use three 2x1 mux, you can create a 4x1 mux. To do this work by using 2x1 mux, write the codes below in Figure 4 by opening a new project.

```

20

library IEEE;

21

use IEEE.STD LOGIC 1164.ALL;

use IEEE.STD LOGIC ARITH.ALL;

22

use IEEE.STD LOGIC UNSIGNED.ALL;

23

24

25

26

entity mux4x1 is

27

Port ( inp : in STD LOGIC VECTOR (3 downto 0);

S : in STD LOGIC VECTOR (1 downto 0);

28

29

outp : out STD LOGIC);

30

end mux4x1;

31

architecture Behavioral of mux4x1 is

32

33

34

component mux2x1 is

35

36

port (

37

a: in STD LOGIC;

38

b: in STD_LOGIC;

39

s: in STD_LOGIC;

40

Y: out STD LOGIC);

41

end component;

42

43

44

signal v,w: STD LOGIC;

45

46

begin

47

48 M1: mux2x1 port map

49

( inp(0), inp(1), S(0), v);

50

51

M2: mux2x1 port map

52

( inp(2), inp(3), S(0), w);

53

54

M3: mux2x1 port map

55

( v, w, S(1), outp);

56

57

end Behavioral;

58

```

#### Figure 4

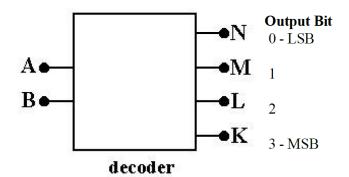

3) A 2 to 4 decoder generates an output signal on its output pins that is dependent on the binary code applied to its inputs. Only one of the output pins is high at any time. For 'n' inputs there will be 2<sup>n</sup> outputs. E.g. 2 to 4, 3 to 8, 4 to 16 etc.

| inputs |   | outputs |   |   |   |

|--------|---|---------|---|---|---|

| Α      | В | K       | L | Μ | Ν |

| 0      | 0 | 0       | 0 | 0 | 1 |

| 0      | 1 | 0       | 0 | 1 | 0 |

| 1      | 0 | 0       | 1 | 0 | 0 |

| 1      | 1 | 1       | 0 | 0 | 0 |

decoder Truth Table

library IEEE; use IEEE.STD LOGIC 1164.ALL; use IEEE.STD LOGIC ARITH.ALL; entity Decoder 24 is Port ( A : in STD LOGIC; B : in STD\_LOGIC; K : out STD\_LOGIC; L : out STD\_LOGIC; M : out STD\_LOGIC; N : out STD LOGIC ); end Decoder\_24; architecture Behavioral of Decoder 24 is begin -- assume that for input A and B that B -- is Least Significant Bit (LSB) -- and for outputs K,L,M, N that N is LSB  $N \le '1'$  when A = '0' and B = '0' else '0';  $M \le '1'$  when A = '0' and B = '1' else '0';  $L \le '1'$  when A = '1' and B = '0' else '0';  $K \le '1'$  when A = '1' and B = '1' else '0'; end Behavioral;

Figure 6

it to verify that this code is working as a 2x4 decoder.

Write the codes in Figure 6 and simulate

Write also a 4x2 encoder and simulate it by using this information.

**Homework 1:** Write 16x1 multiplexer by using 4x1 mux as a component. After writing the codes simulate it and verify the truth table of 16x1 mux.

**Homework 2:** Make a Google search about writing for - loop in vhdl. Then write 3x8 decoder by using for loop. After writing the codes, simulate it.

## Send me whole project folders. (Not screenshots or just codes)

## Deadline: 17.12.2013 Tuesday, 21:00.

No late submission is going to be accepted!

Prepared By: İbrahim BOZKURT e-mail: <u>ibrahimbozkurt@cankaya.edu.tr</u>