## ECE 424 – INTRODUCTION TO VLSI DESIGN + LAB LABORATORY WORK 8

In this laboratory work, we will study on clock division method, Mealy type and Moore type machines.

## **Clock Division:**

When you want to show a counter on your FPGA development card, you cannot see the counting because of its velocity. It will count so fast, because the oscillator frequency of a FPGA development kit is in MHz's. So you should divide clock by using clock division method.

| q(i)   | Frequency (Hz) | Period (ms) |

|--------|----------------|-------------|

| - 4(·) | 50000000.00    | 0.00002     |

| 0      | 25000000.00    | 0.00004     |

| 1      | 12500000.00    | 0.00008     |

| 2      | 6250000.00     | 0.00016     |

| 3      | 3125000.00     | 0.00032     |

| 4      | 1562500.00     | 0.00064     |

| 5      | 781250.00      | 0.00128     |

| 6      | 390625.00      | 0.00256     |

| 7      | 195312.50      | 0.00512     |

| 8      | 97656.25       | 0.01024     |

| 9      | 48828.13       | 0.02048     |

| 10     | 24414.06       | 0.04096     |

| 11     | 12207.03       | 0.08192     |

| 12     | 6103.52        | 0.16384     |

| 13     | 3051.76        | 0.32768     |

| 14     | 1525.88        | 0.65536     |

| 15     | 762.94         | 1.31072     |

| 16     | 381.47         | 2.62144     |

| 17     | 190.73         | 5.24288     |

| 18     | 95.37          | 10.48576    |

| 19     | 47.68          | 20.97152    |

| 20     | 23.84          | 41.94304    |

| 21     | 11.92          | 83.88608    |

| 22     | 5.96           | 167.77216   |

| 23     | 2.98           | 335.54432   |

Figure 1

```

library IEEE;

21

use IEEE.STD LOGIC 1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

22

use IEEE.STD_LOGIC_UNSIGNED.ALL;

23

24

25

entity counter is

26

port ( clk : in std logic;

27

reset : in std logic;

28

pause : in std logic;

count out : out std_logic_vector(3 downto 0));

29

30

end counter;

architecture Behavioral of counter is

31

signal temp count : std logic vector(3 downto 0) := x"0";

signal slow clk : std logic;

33

-- Clock divider can be changed to suit application.

34

-- Clock (clk) is normally 50 MHz, so each clock cycle

35

-- is 20 ns. A clock divider of 'n' bits will make 1

36

37

-- slow clk cycle equal 2^n clk cycles.

38

signal clk_divider : std_logic_vector(23 downto 0) := x"0000000";

-- Process that makes slow clock go high only when MSB of

-- clk divider goes high.

clk division : process (clk, clk divider)

43 begin

44

if (clk = '1' and clk'event) then

45

clk_divider <= clk_divider + 1;

46

end if;

47

slow clk <= clk divider(1);

48

end process;

49

50

counting : process(reset, pause, slow clk, temp count)

51

begin

if reset = '1' then

52

53

temp_count <= "0000"; -- Asynchronous reset.

54

elsif pause = '1' then

55

temp count <= temp count; -- Asynchronous count pause.

56

else

57

if slow clk'event and slow clk ='1' then -- Counting state

58

if temp count < 9 then

59

temp count <= temp count + 1; -- Counter increase

60

61

temp count <= "00000"; -- Rollover to zero

62

end if;

63

end if;

64

end if;

65 count out <= temp_count; -- Output

66 end process;

end Behavioral; -- End module.

```

Figure 2

Figure 1 is explaining the main idea of clock division and figure 2 is giving the vhdl codes for doing this for modulo9 counter. Write the codes and simulate it by using test bench waveform.

## **Moore Machine:**

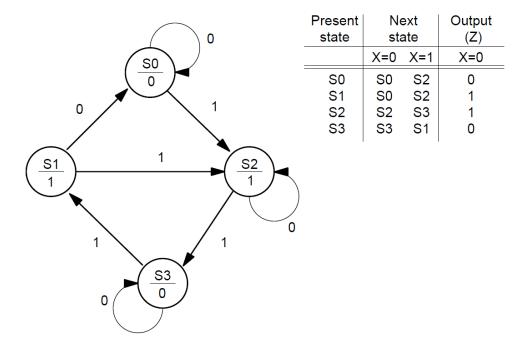

Figure 3

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

20

59

when 82 =>

21

60

z <= '1';

22

if X = '0' then

61

NEXT_STATE <= S2;

62

25

NEXT_STATE <= S3;

26

entity moore is

65

end if;

27

66

when 83 =>

Z <= '0';

if X = '0' then

28

67

port( X, CLOCK: in STD_LOGIC;

29

68

30

Z: out STD_LOGIC);

NEXT_STATE <= S3;

69

31

70

32

end moore;

71

NEXT STATE <= S1;

33

72

end if;

34

architecture Behavioral of moore is

73

end case;

35

74

36

type STATE_TYPE is (S0, S1, S2, S3);

75

end process;

37

signal CURRENT_STATE, NEXT_STATE: STATE_TYPE;

76

38

77

39

78

79

SYNCH: process

40

COMBIN: process(CURRENT_STATE, X)

41

wait until CLOCK'event and CLOCK = '1';

80

42

begin

CURRENT STATE <= NEXT STATE;

81

43

82

end process;

44

case CURRENT STATE is

83

when S0 =>

Z <= '0';

if X = '0' then

45

46

85

end Behavioral;

47

86

48

NEXT_STATE <= S0;

87

else

49

NEXT_STATE <= S2;

50

end if;

51

52

when S1 =>

Z <= '1';

if X = '0' then

53

54

55

NEXT STATE <= SO;

57

NEXT_STATE <= S2;

58

end if;

```

Figure 4

Figure 3 is a simple moore machine Figure 4 is giving vhdl codes of that machine. Write these codes and simulate it.

## **Mealy Machine:**

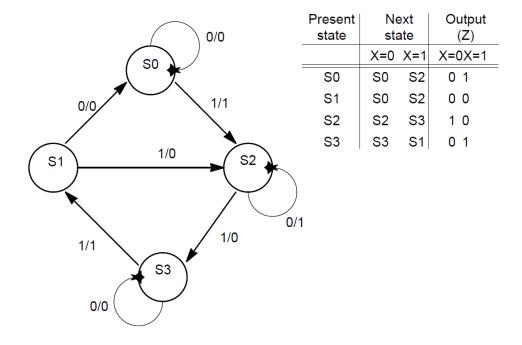

Figure 5

Figure 5 is a FSM(Finite State Machine) that is explaining a simple mealy type machine. Write your own vhdl code for this machine and simulate it to see that your code is working properly.

**Homework:** By using Mealy / Moore machine, design a vending machine, draw the finite state machine diagram and truth table.

Your vending machine is accepting 25Kr, 50Kr and 1 TL. There are three types of drinks in your machine. These drinks are water, ice tea and cola.

The price of cola: 1.50TL

The price of ice tea: 1TL

The price of water: 75 Kr

The customer should choose the drink after giving money. There are 4 buttons on the machine. 3 of them are for cola, ice tea and water. 1 of them is for giving back the money. Don't forget to give back the reminder of money if there is.

Send me FSM diagram and simulated VHDL codes with whole project file.

Deadline: 07.01.2014 Tuesday, 21:00.

Prepared By: İbrahim BOZKURT e-mail: ibrahimbozkurt@cankaya.edu.tr